Estado de soporte técnico de MT3620

Este documento describe el estado actual del soporte de Azure Sphere para MediaTek MT3620. Es posible que también desee hacer referencia al Informe de producto MT3620, que está disponible para su descarga en la página web de MediaTek MT3620. Además, MediaTek produce la Guía de usuario de hardware MT3620, que es una guía detallada para integrar el MCU MT3620 en su propio hardware.

Importante

En el contexto de este documento, no compatible actualmente significa que el uso de la característica por parte del cliente está restringido en el momento actual y es probable que esta restricción se elimine en el futuro. Por el contrario, no es accesible significa que los clientes no pueden usar la característica y es poco probable que esta restricción cambie.

Si tiene solicitudes de características o comentarios, agradecemos sus comentarios en el foro de la comunidad Azure Sphere.

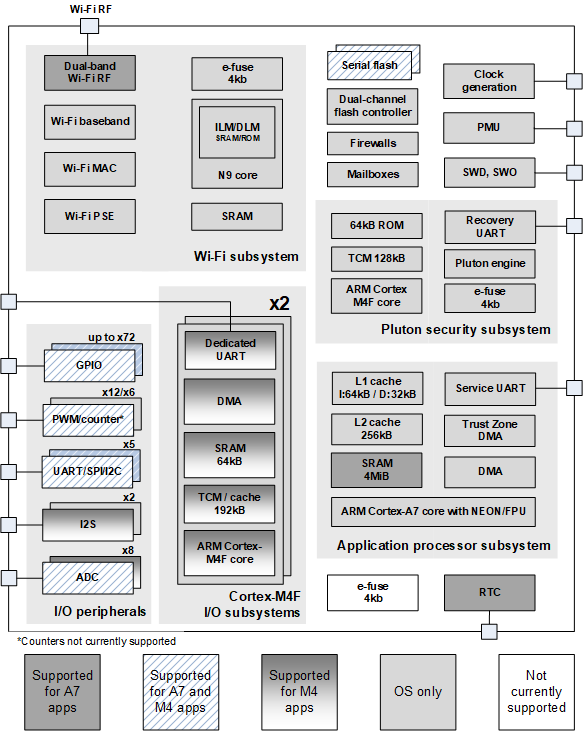

Diagrama de bloques MT3620

El diagrama de bloques muestra la compatibilidad proporcionada para cada componente MT3620. Las secciones que siguen al diagrama proporcionan detalles adicionales sobre estos componentes.

Periféricos de E/S

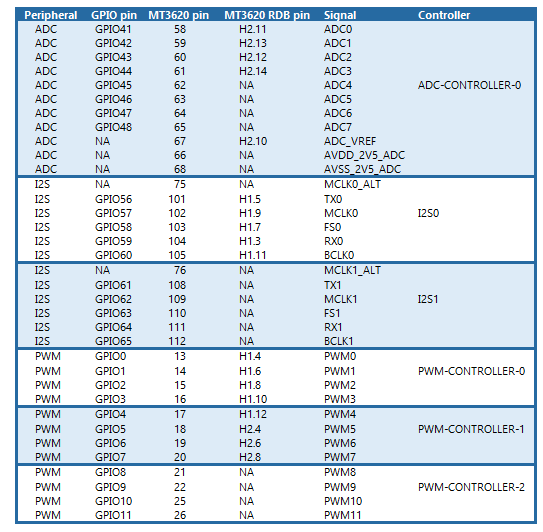

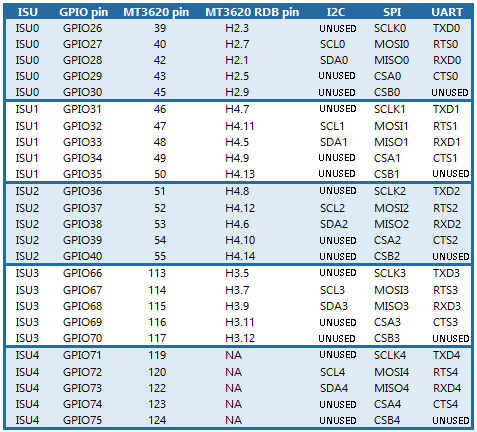

El diseño MT3620 incluye un total de 76 clavijas de E/S programables. Como se muestra en las dos tablas siguientes, la mayoría de los pines se multiplexa entre E/S de uso general (GPIO) y otras funciones. Además de los pin de GPIO enumerados, GPIO12-23 están disponibles en los pines MT3620 27-38 respectivamente.

Haciendo referencia a la tabla siguiente, los pins marcados como "SIN USAR" no son usados por el periférico ISU asociado y se pueden configurar para su uso como pin de GPIO.

Nota

Una vez que se ha asignado un periférico ISU a un núcleo, los 5 pins ISU, incluidos los pins sin usar, están restringidos al uso en ese núcleo.

GPIO/PWM/contadores

Algunas clavijas son multiplexadas entre GPIO, modulación de ancho de pulso (PWM) y contadores de hardware.

Las funciones de GPIO admitidas actualmente son configurar la salida alta/baja y la entrada de lectura. También se admiten los modos de conducción de drenaje/código abierto abiertos y el control de la intensidad de la conducción. Las interrupciones externas se admiten en el núcleo M4, pero no en el núcleo A7.

El MT3620 tiene 12 canales PWM, identificados por PWM0-PWM11. Están organizados en 3 grupos de 4 canales. Cada grupo está asociado con un controlador PWM (PWM-CONTROLLER-0, PWM-CONTROLLER-1, PWM-CONTROLLER-2). Los canales PWM y GPIO anclan GPIO0 a través de GPIO11 mapa a los mismos pines en el MT3620. Si su aplicación utiliza un controlador PWM, todos los pin asociados con ese controlador se asignan para su uso como salidas PWM y ninguno de ellos se puede utilizar para GPIO.

El hardware PWM se puede configurar para usar una de tres frecuencias de reloj fijo: 32 KHz, 2 MHz (XTAL/13) o 26 MHz (XTAL). En los núcleos en tiempo real (RT), una aplicación en tiempo real (RTApp) puede seleccionar qué reloj usar como base. En el núcleo de alto nivel (A7), el controlador de Linux siempre usará el reloj de 2 MHz. Esto da como resultado el ciclo de servicio y las limitaciones de período en aplicaciones de alto nivel, como se explica en El uso de PWMs en aplicaciones de alto nivel.

Bloques de interfaz serie (ISU)

El diseño mt3620 incluye cinco bloques de interfaz serie, cada uno de los cuales contiene cinco pines. (Estos bloques también se denominan ISU, para "I2C, SPI, UART"). Estos bloques de interfaz serie pueden multiplexar GPIO, transmisor asincrónico universal receptor (UART), circuito integrado (I2C) e interfaz de periféricos serie (SPI).

UART es compatible con 1200, 2400, 4800, 9600, 19200, 38400, 57600, 115200, 230400, 460800, 500000, 576000, 921600, 1000000, 1152000, 1500000 y 2000000 baud. Hay un búfer de recepción de hardware de 32 bytes. Se admiten las siguientes opciones de configuración de UART, con 8N1 (8 bits de datos, 1 bit de detención y ninguna paridad) como configuración predeterminada:

- Bit de datos: 5, 6, 7 y 8.

- Bit de detención: 1 y 2.

- Paridad: impar, par y ninguno.

- Modo de control de flujo: RTS/CTS, XON/XOFF, y ningún control de flujo.

Las transacciones SPI son compatibles hasta 40 MHz. Puede conectar hasta dos dispositivos SPI subordinados a cada ISU. Cuando utiliza un puerto ISU como interfaz maestra SPI, no puede utilizar el mismo puerto que una interfaz I2C o UART. Las operaciones SPI de lectura y escritura bidireccional simultáneas (dúplex completo) dentro de una transacción de bus único no son compatibles. Se admiten las siguientes configuraciones de SPI:

- Modo de comunicación (polaridad del reloj, fase del reloj): modo SPI 0 (CPOL = 0, CPHA = 0), modo SPI 1 (CPOL = 0, CPHA = 1), modo SPI 2 (CPOL = 1, CPHA = 0) y modo SPI 3 (CPOL = 1, CPHA = 1).

- Orden de bits: se envía primero el valor menos significativo y el más significativo se envía en primer lugar.

- Polaridad selecta del chip: activo-alto, activo-bajo. Active-low es la configuración predeterminada.

Las direcciones de dispositivo subordinadas de 7 bits son compatibles con I2C. No se admiten direcciones subordinadas I2C de 8 bits o 10 bits. Cuando utiliza un puerto ISU como interfaz maestra I2C, no puede utilizar el mismo puerto que una interfaz SPI o UART. Las lecturas I2C de 0 bytes no son compatibles. Se admiten las siguientes opciones de configuración de I2C:

- Velocidades de bus de 100 KHz, 400 KHz y 1 MHz.

- Tiempo de espera personalizado para operaciones.

I2S

Dos bloques de cinco pines están multiplexados entre GPIO e I2S. Actualmente, I2S solo es compatible con aplicaciones M4.

ADC

El MT3620 contiene un ADC de 12 bits con 8 canales de entrada. Un bloque de ocho pines se multiplexa entre GPIO y el ADC. Los canales de entrada ADC y GPIO ancla GPIO41 a GPIO48 se asignan a las mismas clavijas en el MT3260. Sin embargo, si su aplicación utiliza el ADC, entonces los 8 pins se asignan para su uso como entradas ADC y ninguno de ellos se puede utilizar para GPIO.

Subsistemas ARM Cortex-M4F

El MT3620 incluye dos subsistemas ARM Cortex-M4F de uso general, cada uno de los cuales tiene un bloque dedicado GPIO/UART.

El MT3620 admite una velocidad de reloj predeterminada de 26 MHz. Sin embargo, cada núcleo M4 se puede configurar independientemente para ejecutarse a cualquier velocidad de reloj entre 1 MHz y 200 MHz estableciendo su registro de HCLK_CK_CTRL. El siguiente código muestra una manera de establecer la velocidad de reloj a 200 MHz:

volatile unsigned int *hclk_ck_ctrl = (unsigned int *)0x2101000c;

*hclk_ck_ctrl = 0x00040200;

Nota

Para obtener más información sobre cómo programar los núcleos M4 en el MT3620, consulta la documentación de MT3620 publicada por MediaTek. Si la hoja de datos no contiene toda la información que necesita, envíe un correo electrónico a Avnet (Azure.Sphere@avnet.com) para solicitar la hoja de datos completa.

Los subsistemas ARM Cortex-M4F se pueden programar para admitir interrupciones externas. Consulte Utilizar interrupciones externas en aplicaciones compatibles con tiempo real para obtener más información.

Subsistema de procesador de aplicaciones

El subsistema ARM Cortex-A7 ejecuta una aplicación de cliente junto con el kernel, los servicios y bibliotecas basados en Linux suministrados por Microsoft.

El servicio UART está dedicado a la funcionalidad del sistema para el subsistema A7. No está disponible para el uso de aplicaciones del cliente.

Las aplicaciones de cliente no pueden usar el bloque de fusible electrónico programable de un solo uso, para almacenar información específica del dispositivo.

subsistema de Wi-Fi

El subsistema de Wi-Fi es compatible actualmente con IEEE 802.11 b/g/n a 2,4 GHz y 5 GHz.

Actualmente, Azure Sphere solo admite wpa2, EAP-TLS y autenticación abierta (sin contraseña).

Consulte Herramientas de prueba de RF para obtener información sobre pruebas y calibración de radiofrecuencias.

Control de energía

El MT3620 incluye funciones de apagado y perfil de energía para controlar el consumo de energía. Consulte Consideraciones de Power Down y Consideraciones de power profile para obtener más información.

Relojes y fuentes de alimentación

El cristal principal actualmente solo puede ser de 26 MHz. Las frecuencias de cristal distintas de 26 MHz no son compatibles actualmente con el software.

Detección de color marrón

Actualmente no se admite la detección de brownout.

Temporizadores de perros de vigilancia de hardware

El MTK3620 incluye varios temporizadores de vigilancia:

- Un temporizador de vigilancia dedicado para su uso por el dominio de seguridad plutón. Este temporizador de vigilancia no está disponible para su uso por parte de las aplicaciones.

- Un temporizador de vigilancia disponible para el procesador de aplicaciones. El sistema operativo Azure Sphere usa este temporizador de vigilancia para los servicios del sistema. Este temporizador de vigilancia no está disponible para las aplicaciones.

- Un temporizador de vigilancia para cada uno de los núcleos en tiempo real. Estos temporizadores de vigilancia están disponibles para aplicaciones en tiempo real.

Para obtener más información, vea Usar un temporizador de vigilancia en una RTApp .

SWD, SWO

Serial-wire debug (SWD, pins 98-99) es compatible solamente para aplicaciones M4. La salida de cable de serie (SWO, pin 100) no es compatible actualmente. La depuración de una aplicación A7 es compatible con un mecanismo basado en gdb suministrado por Microsoft.

RAM y flash

El MT3620 incluye aproximadamente 5 MB de RAM en matriz, incluidos 256 KiB en cada subsistema de E/S y 4 MB en el subsistema de aplicación A7.

El MT3620 se puede pedir con 16 MB de memoria flash SPI.

Para obtener información sobre la RAM y flash disponibles para las aplicaciones, consulte Memoria disponible para aplicaciones.

Compatibilidad con pruebas de fabricación

La documentación y las utilidades para apoyar la integración de aplicaciones de prueba de fabricación personalizadas con los procesos de fábrica aún no están disponibles.

Pinout

| Anclar# | Nombre del pin | Funciones principales | Tipo | Descripción | Comentarios |

|---|---|---|---|---|---|

| 1 | GND | P | Tierra | ||

| 2 | AVDD_3V3_WF_A_PA | PI | Guía de potencia de 3,3V para amplificador de potencia de Wi-Fi 5 GHz | ||

| 3 | AVDD_3V3_WF_A_PA | PI | Guía de potencia de 3,3V para amplificador de potencia de Wi-Fi 5 GHz | ||

| 4 | NC | ||||

| 5 | NC | ||||

| 6 | AVDD_1V6_WF_TRX | PI | Guía de alimentación de 1.6V para Wi-Fi transmitir/recibir | ||

| 7 | AVDD_1V6_WF_AFE | PI | Guía de alimentación de 1.6V para Wi-Fi front-end analógico | ||

| 8 | NC | ||||

| 9 | AVDD_1V6_XO | PI | Guía de alimentación de 1.6V para oscilador de cristal principal | ||

| 10 | MAIN_XIN | AI | Entrada de oscilador de cristal principal | ||

| 11 | WF_ANTSEL0 | HACER | selección de antena de Wi-Fi para conmutador DPDT externo | ||

| 12 | WF_ANTSEL1 | HACER | selección de antena de Wi-Fi para conmutador DPDT externo | ||

| 13 | GPIO0 | GPIO0/PWM0 | DIO | GPIO compatible con interrupción multiplexado con salida PWM | |

| 14 | GPIO1 | GPIO1/PWM1 | DIO | GPIO compatible con interrupción multiplexado con salida PWM | |

| 15 | GPIO2 | GPIO2/PWM2 | DIO | GPIO compatible con interrupción multiplexado con salida PWM | |

| 16 | GPIO3 | GPIO3/PWM3 | DIO | GPIO compatible con interrupción multiplexado con salida PWM | |

| 17 | GPIO4 | GPIO4/PWM4 | DIO | GPIO compatible con interrupción multiplexado con salida PWM | |

| 18 | GPIO5 | GPIO5/PWM5 | DIO | GPIO compatible con interrupción multiplexado con salida PWM | |

| 19 | GPIO6 | GPIO6/PWM6 | DIO | GPIO compatible con interrupción multiplexado con salida PWM | |

| 20 | GPIO7 | GPIO7/PWM7 | DIO | GPIO compatible con interrupción multiplexado con salida PWM | |

| 21 | GPIO8 | GPIO8/PWM8 | DIO | GPIO compatible con interrupción multiplexado con salida PWM | |

| 22 | GPIO9 | GPIO9/PWM9 | DIO | GPIO compatible con interrupción multiplexado con salida PWM | |

| 23 | DVDD_1V15 | PI | Guía de alimentación de 1.15V | ||

| 24 | DVDD_3V3 | PI | Guía de alimentación de 3.3V | ||

| 25 | GPIO10 | GPIO10/PWM10 | DIO | GPIO compatible con interrupción multiplexado con salida PWM | |

| 26 | GPIO11 | GPIO11/PWM11 | DIO | GPIO compatible con interrupción multiplexado con salida PWM | |

| 27 | GPIO12 | DIO | GPIO compatible con interrupciones | Las interrupciones no son compatibles actualmente | |

| 28 | GPIO13 | DIO | GPIO compatible con interrupciones | Las interrupciones no son compatibles actualmente | |

| 29 | GPIO14 | DIO | GPIO compatible con interrupciones | Las interrupciones no son compatibles actualmente | |

| 30 | GPIO15 | DIO | GPIO compatible con interrupciones | Las interrupciones no son compatibles actualmente | |

| 31 | GPIO16 | DIO | GPIO compatible con interrupciones | Las interrupciones no son compatibles actualmente | |

| 32 | GPIO17 | DIO | GPIO compatible con interrupciones | Las interrupciones no son compatibles actualmente | |

| 33 | GPIO18 | DIO | GPIO compatible con interrupciones | Las interrupciones no son compatibles actualmente | |

| 34 | GPIO19 | DIO | GPIO compatible con interrupciones | Las interrupciones no son compatibles actualmente | |

| 35 | GPIO20 | DIO | GPIO compatible con interrupciones | Las interrupciones no son compatibles actualmente | |

| 36 | GPIO21 | DIO | GPIO compatible con interrupciones | Las interrupciones no son compatibles actualmente | |

| 37 | GPIO22 | DIO | GPIO compatible con interrupciones | Las interrupciones no son compatibles actualmente | |

| 38 | GPIO23 | DIO | GPIO compatible con interrupciones | Las interrupciones no son compatibles actualmente | |

| 39 | GPIO26 | GPIO26/ SCLK0/TXD0 | DIO | GPIO multiplexado con funciones ISU 0 | |

| 40 | GPIO27 | GPIO27/ MOSI0/RTS0/SCL0 | DIO | GPIO multiplexado con funciones ISU 0 | |

| 41 | GND | P | Tierra | ||

| 42 | GPIO28 | GPIO28/ MISO0/RXD0/SDA0 | DIO | GPIO multiplexado con funciones ISU 0 | |

| 43 | GPIO29 | GPIO29/CSA0/CTS0 | DIO | GPIO multiplexado con funciones ISU 0 | |

| 44 | DVDD_1V15 | PI | Guía de alimentación de 1.15V | ||

| 45 | GPIO30 | GPIO30/CSB0 | DIO | GPIO multiplexado con funciones ISU 0 | |

| 46 | GPIO31 | GPIO31/ SCLK1/TXD1 | DIO | GPIO multiplexado con funciones ISU 1 | |

| 47 | GPIO32 | GPIO32/ MOSI1/RTS1/SCL1 | DIO | GPIO multiplexado con funciones ISU 1 | |

| 48 | GPIO33 | GPIO33/ MISO1/RXD1/SDA1 | DIO | GPIO multiplexado con funciones ISU 1 | |

| 49 | GPIO34 | GPIO34/CSA1/CTS1 | DIO | GPIO multiplexado con funciones ISU 1 | |

| 50 | GPIO35 | GPIO35/CSB1 | DIO | GPIO multiplexado con funciones ISU 1 | |

| 51 | GPIO36 | GPIO36/ SCLK2/TXD2 | DIO | GPIO multiplexado con funciones ISU 2 | |

| 52 | GPIO37 | GPIO37/MOSI2/RTS2/SCL2 | DIO | GPIO multiplexado con funciones ISU 2 | |

| 53 | GPIO38 | GPIO38/ MISO2/RXD2/SDA2 | DIO | GPIO multiplexado con funciones ISU 2 | |

| 54 | GPIO39 | GPIO39/CSA2/CTS2 | DIO | GPIO multiplexado con funciones ISU 2 | |

| 55 | GPIO40 | GPIO40/CSB2 | DIO | GPIO multiplexado con funciones ISU 2 | |

| 56 | DVDD_3V3 | PI | Guía de alimentación de 3.3V | ||

| 57 | DVDD_1V15 | PI | Guía de alimentación de 1.15V | ||

| 58 | GPIO41 | GPIO41/ADC0 | DIO | GPIO multiplexado con entrada ADC | |

| 59 | GPIO42 | GPIO42/ADC1 | DIO | GPIO multiplexado con entrada ADC | |

| 60 | GPIO43 | GPIO43/ADC2 | DIO | GPIO multiplexado con entrada ADC | |

| 61 | GPIO44 | GPIO44/ADC3 | DIO | GPIO multiplexado con entrada ADC | |

| 62 | GPIO45 | GPIO45/ADC4 | DIO | GPIO multiplexado con entrada ADC | |

| 63 | GPIO46 | GPIO46/ADC5 | DIO | GPIO multiplexado con entrada ADC | |

| 64 | GPIO47 | GPIO47/ADC6 | DIO | GPIO multiplexado con entrada ADC | |

| 65 | GPIO48 | GPIO48/ADC7 | DIO | GPIO multiplexado con entrada ADC | |

| 66 | AVDD_2V5_ADC | PI | Guía de alimentación de 2.5V para ADC | ||

| 67 | VREF_ADC | AI | Tensión de referencia para ADC | ||

| 68 | AVSS_2V5_ADC | P | Terreno para ADC | ||

| 69 | EXT_PMU_EN | HACER | La fuente de alimentación externa habilita la salida | ||

| 70 | ACTIVACIÓN | DI | Reactivación externa desde el modo de suspensión más profundo | No se admite actualmente | |

| 71 | AVDD_3V3_RTC | PI | Guía de alimentación de 3.3V para reloj en tiempo real | ||

| 72 | RTC_XIN | AI | Entrada oscilador de cristal del reloj en tiempo real | ||

| 73 | RTC_XOUT | AO | Salida del oscilador de cristal del reloj en tiempo real | ||

| 74 | AVDD_3V3_XPPLL | PI | Guía de alimentación de 3.3V para bucle interno bloqueado por fases | ||

| 75 | I2S_MCLK0_ALT | AO | Alternativa analógica a MCLK0 | Actualmente, I2S solo es compatible con aplicaciones M4. | |

| 76 | I2S_MCLK1_ALT | AO | Alternativa analógica a MCLK1 | Actualmente, I2S solo es compatible con aplicaciones M4. | |

| 77 | DVDD_1V15 | PI | Guía de alimentación de 1.15V | ||

| 78 | DVDD_1V15 | PI | Guía de alimentación de 1.15V | ||

| 79 | VOUT_2V5 | PO | Salida desde LDO interno de 2,5V | ||

| 80 | AVDD_3V3 | PI | Guía de alimentación de 3.3V | ||

| 81 | PMU_EN | DI | Invalidación de PMU interna | ||

| 82 | RESERVADOS | ||||

| 83 | GND | P | Tierra | ||

| 84 | SENSE_1V15 | AI | Entrada de sensor para estabilizar la fuente de alimentación de 1,15 V | ||

| 85 | VOUT_1V15 | PO | Salida desde LDO interno de 1,15V | ||

| 86 | AVDD_1V6_CLDO | PI | Guía de alimentación de 1.6V para el LDO interno de 1.15V | ||

| 87 | PMU_CAP | Un | Conectar un condensador entre este pin y AVDD_3V3_BUCK para mantener la estabilidad PMU | ||

| 88 | AVDD_3V3_BUCK | PI | Guía de alimentación de 3.3V para convertidor interno de CC-CC de buck de 1.6V | ||

| 89 | AVDD_3V3_BUCK | PI | Guía de alimentación de 3.3V para convertidor interno de CC-CC de buck de 1.6V | ||

| 90 | VOUT_1V6 | PO | Salida del convertidor de buck interno de 1.6V | ||

| 91 | VOUT_1V6 | PO | Salida del convertidor de buck interno de 1.6V | ||

| 92 | AVSS_3V3_BUCK | P | Ground for internal 1.6V buck converter | ||

| 93 | AVSS_3V3_BUCK | P | Ground for internal 1.6V buck converter | ||

| 94 | DEBUG_RXD | DI | Reservado para depuración de Azure Sphere | ||

| 95 | DEBUG_TXD | HACER | Reservado para depuración de Azure Sphere | ||

| 96 | DEBUG_RTS | HACER | Reservado para depuración de Azure Sphere | ||

| 97 | DEBUG_CTS | DI | Reservado para depuración de Azure Sphere | ||

| 98 | SWD_DIO | DIO | ARM SWD para depuración cortex-M4F | ||

| 99 | SWD_CLK | DI | ARM SWD para depuración cortex-M4F | ||

| 100 | SWO | HACER | ARM SWO para depuración cortex-M4F | No se admite actualmente | |

| 101 | GPIO56 | GPIO56/TX0 | DIO | GPIO multiplexado con I2S 0 | Actualmente, I2S solo es compatible con aplicaciones M4. |

| 102 | GPIO57 | GPIO57 /MCLK0 | DIO | GPIO multiplexado con I2S 0 | Actualmente, I2S solo es compatible con aplicaciones M4. |

| 103 | GPIO58 | GPIO58/FS0 | DIO | GPIO multiplexado con I2S 0 | Actualmente, I2S solo es compatible con aplicaciones M4. |

| 104 | GPIO59 | GPIO59/RX0 | DIO | GPIO multiplexado con I2S 0 | Actualmente, I2S solo es compatible con aplicaciones M4. |

| 105 | GPIO60 | GPIO60/ BCLK0 | DIO | GPIO multiplexado con I2S 0 | Actualmente, I2S solo es compatible con aplicaciones M4. |

| 106 | DVDD_1V15 | PI | Guía de alimentación de 1.15V | ||

| 107 | DVDD_3V3 | PI | Guía de alimentación de 3.3V | ||

| 108 | GPIO61 | GPIO61/TX1 | DIO | GPIO multiplexado con I2S 1 | Actualmente, I2S solo es compatible con aplicaciones M4. |

| 109 | GPIO62 | GPIO62/ MCLK1 | DIO | GPIO multiplexado con I2S 1 | Actualmente, I2S solo es compatible con aplicaciones M4. |

| 110 | GPIO63 | GPIO63/FS1 | DIO | GPIO multiplexado con I2S 1 | Actualmente, I2S solo es compatible con aplicaciones M4. |

| 111 | GPIO64 | GPIO64/RX1 | DIO | GPIO multiplexado con I2S 1 | Actualmente, I2S solo es compatible con aplicaciones M4. |

| 112 | GPIO65 | GPIO65/ BCLK1 | DIO | GPIO multiplexado con I2S 1 | Actualmente, I2S solo es compatible con aplicaciones M4. |

| 113 | GPIO66 | GPIO66/ SCLK3/TXD3 | DIO | GPIO multiplexado con funciones ISU 3 | |

| 114 | GPIO67 | GPIO67/ MOSI3/RTS3/SCL3 | DIO | GPIO multiplexado con funciones ISU 3 | |

| 115 | GPIO68 | GPIO68/ MISO3/RXD3/SDA3 | DIO | GPIO multiplexado con funciones ISU 3 | |

| 116 | GPIO69 | GPIO69/CSA3/CTS3 | DIO | GPIO multiplexado con funciones ISU 3 | |

| 117 | GPIO70 | GPIO70/CSB3 | DIO | GPIO multiplexado con funciones ISU 3 | Actualmente solo es compatible con GPIO |

| 118 | DVDD_3V3 | PI | Guía de alimentación de 3.3V | ||

| 119 | GPIO71 | GPIO71/ SCLK4/TXD4 | DIO | GPIO multiplexado con funciones ISU 4 | |

| 120 | GPIO72 | GPIO72/ MOSI4/RTS4/SCL4 | DIO | GPIO multiplexado con funciones ISU 4 | |

| 121 | DVDD_1V15 | PI | Guía de alimentación de 1.15V | ||

| 122 | GPIO73 | GPIO73/ MISO4/RXD4/SDA4 | DIO | GPIO multiplexado con funciones ISU 4 | |

| 123 | GPIO74 | GPIO74/CSA4/CTS4 | DIO | GPIO multiplexado con funciones ISU 4 | |

| 124 | GPIO75 | GPIO75/CSB4 | DIO | GPIO multiplexado con funciones ISU 4 | |

| 125 | SYSRST_N | DI | Restablecimiento del sistema, mínimo activo | ||

| 126 | DVDD_1V15 | PI | Guía de alimentación de 1.15V | ||

| 127 | SERVICE_TXD | HACER | Puerto de servicio Azure Sphere | No disponible para el uso de aplicaciones del cliente | |

| 128 | SERVICE_RTS | HACER | Puerto de servicio Azure Sphere | No disponible para el uso de aplicaciones del cliente | |

| 129 | SERVICE_RXD | DI | Puerto de servicio Azure Sphere | No disponible para el uso de aplicaciones del cliente | |

| 130 | SERVICE_CTS | DI | Puerto de servicio Azure Sphere | No disponible para el uso de aplicaciones del cliente | |

| 131 | RESERVADOS | ||||

| 132 | DVDD_1V15 | PI | Guía de alimentación de 1.15V | ||

| 133 | DVDD_3V3 | PI | Guía de alimentación de 3.3V | ||

| 134 | RECOVERY_RXD | DI | Puerto de recuperación de Azure Sphere | No disponible para el uso de aplicaciones del cliente | |

| 135 | RECOVERY_TXD | HACER | Puerto de recuperación de Azure Sphere | No disponible para el uso de aplicaciones del cliente | |

| 136 | RECOVERY_RTS | HACER | Puerto de recuperación de Azure Sphere | No disponible para el uso de aplicaciones del cliente | |

| 137 | RECOVERY_CTS | DI | Puerto de recuperación de Azure Sphere | No disponible para el uso de aplicaciones del cliente | |

| 138 | IO0_GPIO85 | IO0_GPIO85/IO0_RXD | DI | GPIO dedicado multiplexado con UART para I/O M4 0 | |

| 139 | IO0_GPIO86 | IO0_GPIO86/IO0_TXD | HACER | GPIO dedicado multiplexado con UART para I/O M4 0 | |

| 140 | IO0_GPIO87 | IO0_GPIO87/IO0_RTS | HACER | GPIO dedicado multiplexado con UART para I/O M4 0 | |

| 141 | IO0_GPIO88 | IO0_GPIO88/IO0_CTS | DI | GPIO dedicado multiplexado con UART para I/O M4 0 | |

| 142 | IO1_GPIO89 | IO1_GPIO89/IO1_RXD | DI | GPIO dedicado multiplexado con UART para I/O M4 1 | |

| 143 | IO1_GPIO90 | IO1_GPIO90/IO1_TXD | HACER | GPIO dedicado multiplexado con UART para I/O M4 1 | |

| 144 | DVDD_3V3 | PI | Guía de alimentación de 3.3V | ||

| 145 | IO1_GPIO91 | IO1_GPIO91/IO1_RTS | HACER | GPIO dedicado multiplexado con UART para I/O M4 1 | |

| 146 | IO1_GPIO92 | IO1_GPIO92/IO1_CTS | DI | GPIO dedicado multiplexado con UART para I/O M4 1 | |

| 147 | RESERVADOS | ||||

| 148 | PRUEBA | DI | Debe extraerse con poca carga para un funcionamiento normal | ||

| 149 | WF_G_RF_AUXIN | RF | Los Wi-Fi de 2,4 GHz reciben un puerto de diversidad | ||

| 150 | NC | ||||

| 151 | AVDD_3V3_WF_G_PA | PI | Guía de alimentación de 3,3V para amplificador de potencia de Wi-Fi 2,4 GHz | ||

| 152 | NC | ||||

| 153 | WF_G_RF_ION | RF | Puerto de antena de Wi-Fi de 2,4 GHz (diferencial) | ||

| 154 | WF_G_RF_ION | RF | Puerto de antena de Wi-Fi de 2,4 GHz (diferencial) | ||

| 155 | WF_G_RF_IOP | RF | Puerto de antena de Wi-Fi de 2,4 GHz (diferencial) | ||

| 156 | WF_G_RF_IOP | RF | Puerto de antena de Wi-Fi de 2,4 GHz (diferencial) | ||

| 157 | NC | ||||

| 158 | AVDD_3V3_WF_G_TX | PI | Guía de alimentación de 3,3V para transmisión de potencia de 2,4 GHz Wi-Fi | ||

| 159 | WF_A_RF_AUXIN | RF | Los Wi-Fi de 5 GHz reciben puerto de diversidad | ||

| 160 | AVDD_3V3_WF_A_TX | PI | Guía de alimentación de 3,3V para 5 GHz Wi-Fi transmisión de energía | ||

| 161 | NC | ||||

| 162 | WF_A_RFIO | RF | Puerto de antena de Wi-Fi de 5 GHz (desequilibrado) | ||

| 163 | WF_A_RFIO | RF | Puerto de antena de Wi-Fi de 5 GHz (desequilibrado) | ||

| 164 | GND | P | Tierra | ||

| 165 | EPAD | P | Tierra |